1.时钟约束修复 分析建立时间用慢速模型:高温、低压、慢速模型(最差情况) 分析保持时间用快速模型:...注意时钟频率无法解决,保持时间公式里没有T,与T无关。 4.clock skew和clock jitter 时钟抖动(Clock Jitter

”结构与管道同步工程 图的时序传播 并行静态时序分析 任务图并行“ 的搜索结果

OpenTimer是一个新的静态时序分析(STA)工具,可帮助IC设计人员快速验证电路时序。 它是OpenTimer VLSI系统的高性能时序分析工具,为什么选择OpenTimer? OpenTimer是一个新的静态时序分析(STA)工具,可帮助IC...

摘要:提出了一种分段式双通道高速数据采集系统的设计方案。对其中高速A/D、高速存储、智能控制以及接口译码等模块...系统内含两路羡并行采样通道,因其器件参数、控制时序完全一致,可实现双通道同步采集数据,满足

(1)华为:静态时序分析与逻辑设计 (2)王敏志:FPGA设计实战演练(高级技巧篇) 【FPGA探索者】公众号内回复【关键路径】获取两个资料。 关键路径通常是指同步逻辑电路中,组合逻辑时延最大的路径(这里我...

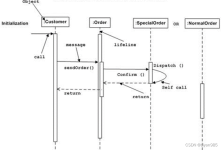

文章目录顺序图(时序图)顺序图的引入顺序图的概念顺序图的组成①对象( Object)②生命线( Lifeline )③激活(Activation) (控制焦点focus of control)④消息(Message)消息的表示和分类调用消息(Procedure Call)异步...

1、静态时序分析基础 2、基本的同步时序路径约束 建立时间,保持时间 为了确保寄存器在时钟沿稳定采集数据,那么必须要满足寄存器的建立,保持时间要求。 建立时间要求:在寄存器有效时钟沿之前至少Tsetup时间,数据...

本文用通俗语言详细讲解软件工程面向对象分析建模的知识

序列图捕获:在实现用例或操作的协作中发生的交互(实例图或通用图)系统用户与系统之间,系统与其他系统之间或子系统之间的高级交互(有时称为系统序列图)序列图的目的模拟系统中生成的对象之间的高级...

当与一个比任务级并行更容易编程且可能具有更高能效的模型相结合时,就很容易理解为什么在这十年中数据级并行出现了复兴。传统处理器与GPU在性能方面最大的差别之一是集中--分散寻址。GPU的问题不只是哪种体系结构...

时序就是时钟序列,给寄存器作为数据的传递 时钟和复位是属于异步的关系 LUT查找表,所以的组合逻辑都是靠它生成,时序逻辑是靠触发器生成 一个LAB(单元)里面有16个LE(根据器件不同应该不同吧) RAM是FPGA里面的...

我们在画时序图时会涉及7种元素:角色(Actor)、对象(Object)、生命线(LifeLine)、控制焦点(Activation)、消息(Message)、自关联消息、组合片段。其中前6种是比较常用和重要的元素,剩余的一种组合片段元素不是很常用...

静态模型包括类图与ER图,主要是描述存在系统中静态资源的存储形式 用例图 用例图是被称为参与者的外部用户所能观察到的系统功能的模型图,用例图列出系统中的用例和系统外的参与者,并显示哪个参与者参与了哪个用例...

并行与分布式 第七章 体系结构 上

标签: 分布式

多核CPU采用了与原来的单CPU相同的硬件体系结构,显著提升计算能力的同时无需进行硬件技术的变更。• 当出现某cache块被替换写回时,被写回的旧块有唯一目录节点B1,被调入的新块有唯一目录节点B2,cache和B1、B2都...

【设计相关】UML类图和时序图介绍

标签: uml

统一建模语言(Unified Modeling Language,UML)是一种为面向对象系统的产品进行说明、可视化和编制文档的一种标准语言,是非专利的第三代建模和规约语言。UML 使用面向对象设计的的建模工具,但独立于任何具体...

TDengine 的设计是基于单个硬件、软件系统不可靠,基于任何单台计算机都无法提供足够计算能力和存储能力处理海量数据的假设进行设计的。...TDengine 分布式架构的逻辑结构图如下:图 1 TDengine架构示意图一个完整

推荐文章

- Unity3D 导入资源_unity怎么导入压缩包-程序员宅基地

- jqgrid 服务器端验证,javascript – jqgrid服务器端错误消息/验证处理-程序员宅基地

- 白山头讲PV: 用calibre进行layout之间的比对-程序员宅基地

- java exit方法_Java:如何测试调用System.exit()的方法?-程序员宅基地

- 如何在金山云上部署高可用Oracle数据库服务_rman target sys/holyp#ssw0rd2024@gdcamspri auxilia-程序员宅基地

- Spring整合Activemq-程序员宅基地

- 语义分割入门的总结-程序员宅基地

- SpringBoot实践(三十五):JVM信息分析_怎样查看springboot项目的jvm状态-程序员宅基地

- 基于springboot+vue的戒毒所人员管理系统 毕业设计-附源码251514_戒毒所管理系统-程序员宅基地

- 【LeetCode】面试题57 - II. 和为s的连续正数序列_leet code 和为s的正数序列 java-程序员宅基地